AM1808EZWT3 Original And New With Competitive Price In Stock IC Supplier

Product Attributes

| TYPE | ILLUSTRATE |

CHOOSE |

| category | Integrated Circuits (ICs) |

|

| manufacturer | Texas Instruments |

|

| series | Sitara™ |

|

| wrap | tray |

|

| Product status | Active |

|

| Core processor | ARM926EJ-S |

|

| Number of cores/bus width | 1 I-core, 32-bit |

|

| velocity | 375MHz |

|

| Secondary processor/DSP | System control; CP15 |

|

| RAM controller | LPDDR、DDR2 |

|

| Graphics acceleration | not |

|

| Display and interface controllers | LCD |

|

| Ethernet | 10/100Mbps (1) |

|

| HOURS | SATA 3Gbps (1) |

|

| USB | USB 1.1 + PHY (1)、USB 2.0 + PHY (1) |

|

| Voltage - I/O | 1.8V、3.3V |

|

| Operating temperature | 0°C ~ 90°C(TJ) |

|

| Security features | - |

|

| Installation type | Surface adhesive type |

|

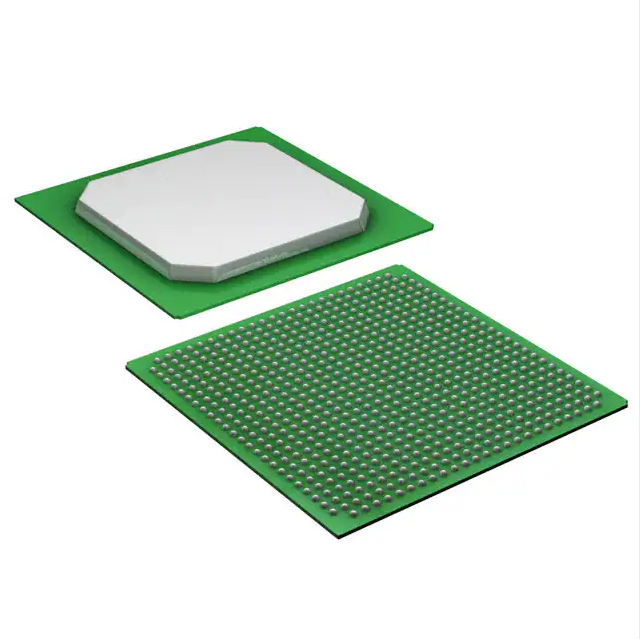

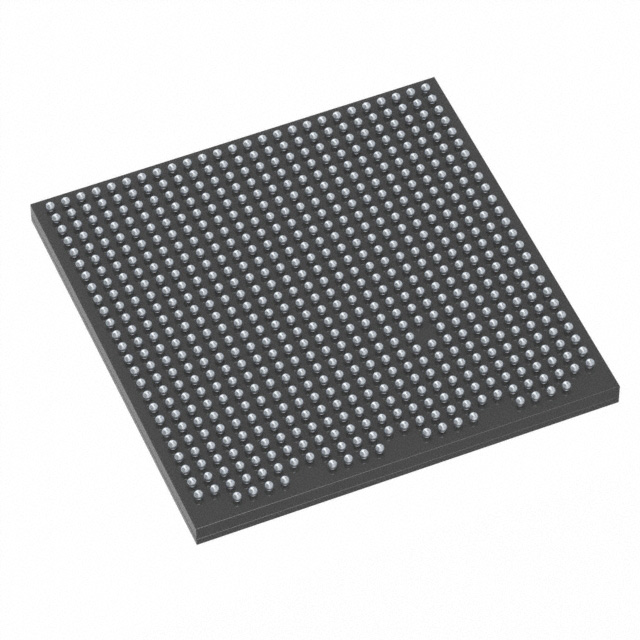

| Package/Housing | 361-LFBGA |

|

| Vendor component encapsulation | 361-NFBGA (16x16) |

|

| Additional interface | I²C、McASP、McBSP、SPI、MMC/SD、UART |

|

| Product master number | AM1808 |

Integrated Circuit Type

The 16-bit microprocessor can be divided into two parts, one part is the execution unit (EU), which is the part that executes instructions; the other part is the bus interface unit (BIU), which is connected to the 8086 bus and executes the operation of fetching instructions from the memory. After the microprocessor is divided into EU and BIU, the operations of fetching instructions and executing instructions can be overlapped. The EU part has a register file, which consists of 8 16-bit registers, which can be used to store data, index and stack pointer, arithmetic operation logic unit (ALU) to perform arithmetic operations and logic operations, and flag registers to store the conditions of the results of these operations. These units in the execution unit transfer data through the data bus. The bus interface unit also has a register file, where CS, DS, SS, and ES are segment registers for memory space segmentation. IP is the instruction pointer. The internal communication register is also a register for temporarily storing data. The command queue is to store the pre-fetched command stream. The bus interface part also has an address adder, which adds the segment register value and offset value to obtain a 20-bit physical address. Data and addresses are connected with the external 8086 system bus through the bus control logic. The 8086 has a 16-bit data bus. When the processor and the off-chip transmit data, a 16-bit binary number is transmitted in one class. 8086 has a primary pipeline structure, which can realize the overlap of on-chip operations and off-chip operations.