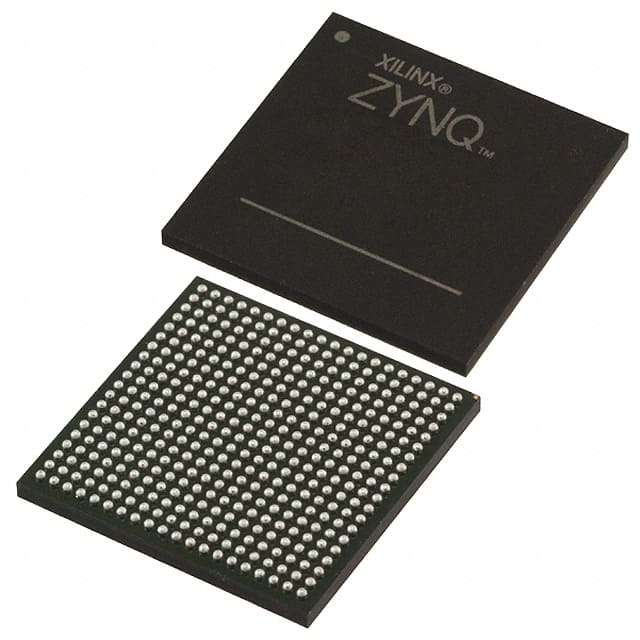

XCKU15P-2FFVE1760E 100% new and original stock

Product Introduction

This brand of FPGA series has excellent cost performance, performance, power consumption, and provides high-end functions, such as transceivers, memory interface line rates, 100G connection chips, etc. FPGA selectable -3, -2, -1 speed grades. This series is ideal for packet processing, DSP functions, and applications such as wireless MIMO technology, Nx100G networks and data centers. The device adopts UltraScale™ architecture, which has ultra-high performance, with on-chip UltraRAM memory, which can reduce BOM cost, and can cooperate with high-performance peripherals to create cost-effective systems. FPGAs have a variety of power supply options, balancing system performance with required power.

Recommended Operating Conditions

Normally recommends measuring the Tj of a device using the system monitor as described in the UltraScale Architecture System Monitor User Guide (UG580). The system monitor temperature measurement errors (that are described in Table 78) must be accounted for in your design. For example, when using the system monitor with an external reference of 1.25V, and when the system monitor reports 97°C, there is a measurement error ±3°C. A reading of 97°C is considered the maximum adjusted Tj (100°C – 3°C = 97°C).

Devices labeled with the speed/temperature grade of -2LE can operate for a limited time at a junction temperature between 100°C and 110°C. Timing parameters adhere to the same speed file at 110°C as they do below 110°C, regardless of operating voltage (nominal voltage of 0.85V or a low-voltage of 0.72V). Operation up to Tj= 110°C is limited to 1% of the device lifetime and can occur sequentially or at regular intervals as long as the total time does not exceed 1% of the device lifetime.

Do not program eFUSE during device configuration (e.g., during configuration, during configuration readback, or when readback CRC is active).

.png)